Electronic Design Automation (EDA) tools are widely used in circuit design and greatly assist designers in handling the complexities and challenges of circuit design and evaluation.

There have been numerous recent developments in using machine learning tools, particularly Graph Neural Networks (GNNs), to address circuit design problems. These techniques take advantage of the natural representation of a circuit as a graph. In this study, we propose using state-of-the-art GNNs to solve a key circuit design issue.

Specifically, we are interested in addressing the Circuit Completion Problem (CCP), where the goal is to determine the missing components and their connections in a partially designed or evaluated circuit.

We provide a novel two-step solution to this problem: first, we formulate missing component identification as a graph classification task in the graph-based representation of partial circuit, and second, we treat the placement and connectivity of the newly (predicted) component as a link completion problem.

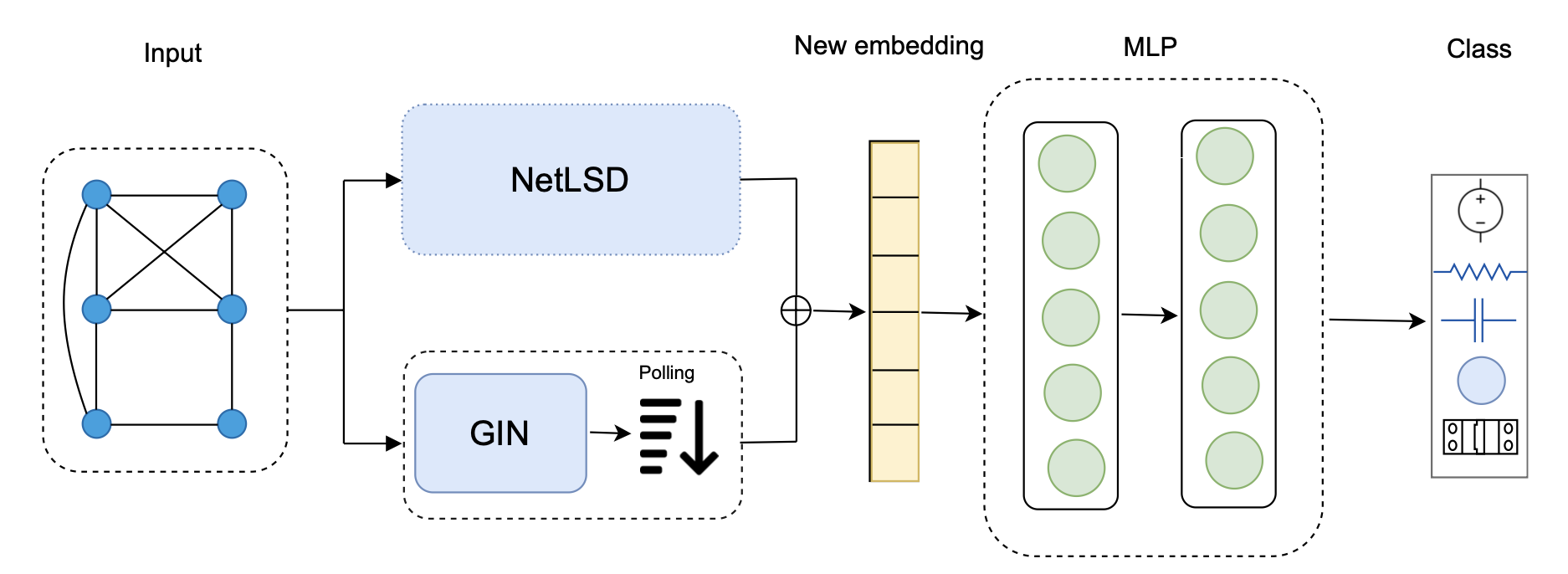

We propose a novel graph learning framework called Feature Enhanced Graph Isomorphism Network (FEGIN) that combines both GNNs and graph descriptors in an end-to-end fashion to extract expressive graph representations.

We also present three new circuit datasets to implement and test our solutions. Our extensive experiments demonstrate that the proposed framework is an effective and generalizable solution to the CCP problem.

The source code and datasets of this paper are made publicly available.